摘要

在过去几十年中,人们主要通过不断的缩小CMOS技术的工艺尺寸的方式,来提高芯片的性能和集成密度,并降低功耗。然而,随着CMOS器件尺寸越来越接近其物理极限,对具有与传统CMOS不同工作原理的新型器件的探索需求不断增加。近年来,许多努力致力于研究基于下一代新型非易失性存储器(Emergingnon-volatilememory)的类脑神经形态计算技术,如:阻变存储器,相变存储器和磁存储器等。其中,忆阻具有高速、高密度、低功耗、易集成、与CMOS工艺兼容等优点,且被认为可以精确模拟突触可塑性行为,因此,极具潜力成为神经形态计算系统中的基本突触单元。

具有模拟特性的忆阻器阵列能够进行并行的矩阵向量乘法运算和权重更新操作,这可以显着的缩短人工神经网络算法的训练时间。但是,非理想的忆阻器件模拟性能往往会对神经网络学习的准确性造成影响。因此,阐明忆阻器件的非理想模拟特性对神经网络学习准确性的影响规律,对于进一步优化器件性能、发展相应网络硬件算法,至关重要。

本文首先基于忆阻器件模拟特性的实验数据,统计建立了忆阻器电导渐变曲线的数学模型,并通过模型中的参数拟合来量化忆阻器的非理想特性参数。其次,为了将神经网络学习算法映射到忆阻器阵列中,本文根据忆阻阵列实现并行矩阵向量乘法运算的基本原理,设计了阵列中器件电导与突触权重之间的映射方式,阵列输入信息的编码方式和外围电路的基本模块。随后基于C++编程语言编写了忆阻器突触硬件模块的仿真程序,实现了2层的感知机神经网络模型和随机梯度下降算法到硬件模块的映射过程。最后,实现了针对MNIST手写字体数据集的忆阻器神经网络的训练和推断验证,分别探讨了离线学习和在线学习过程中,忆阻器的非理想参数,包括电导渐变调控的非线性、电导窗口比、电导阶数、循环一致性、器件间一致性、读噪声、以及阵列中忆阻器件失效比率等,对神经网络学习识别率的影响,从而提出面向硬件神经形态系统的忆阻器突触器件后续优化方向。

关键词:忆阻器,人工突触,多层感知机,神经网络手,写字体识别

Abstract

Over the past few decades, the silicon complementary-metal-oxide-semiconductor (CMOS) technology has been greatly scaled down to achieve higher performance, density and lower power consumption. However, as the device dimension is approaching its fundamental physical limit, there is an increasing demand for exploration of emerging devices with distinct operating principles from conventional CMOS. In recent years, many efforts have been devoted to the research of brain-inspired neuromorphic computing technologies based on the next generation of Emerging non-volatile memory, such as resistive memory, phase change memory and magnetic memory. As one of the emerging non-volatile device, memristor has the advantages of high speed, high density, low power consumption, easy integration, compatibility with CMOS technology, and is considered to accurately simulate synaptic plasticity behavior. Therefore, it is the basic synaptic unit in the highly promising neuromorphic computing system.

Memristor arrays with analog characteristics can enable parallel matrix vector multiplication and weight update operations, which can significantly shorten the training time of artificial neural network algorithms. However, the performance of non-ideal analog memristive devices tends to affect the accuracy of neural network learning algorithms. Therefore, clarifying the influence of the performance of non-ideal analog memristive devices on the learning accuracy of neural networks is crucial for further optimizing device performance and developing corresponding network hardware algorithms.

In this thesis, based on the experimental data of the memristive device analog characteristics, the mathematical model of the memristor conductance analog tuning curve is established statistically, and the non-ideal characteristic parameters of the memristor are quantified by parameter fitting in the model. Secondly, in order to map the neural network learning algorithm to the memristor array, this thesis designs the mapping method between device conductance and synaptic weight in the array, the encoding method of the input information and the basic module of the peripheral circuit according to the basic principle of parallel matrix vector multiplication operation in the memristor array. Then, based on the C++ programming language, a simulation program based on the memristor synaptic hardware module is written, which realizes the mapping process of the two-layer perceptron neural network model and the stochastic gradient descent algorithm. Finally, the training and inference verification of memristor neural network based on MNIST handwritten font dataset are realized. The influence of memristor's non-ideal parameters, including the nonlinearity, number of conductance states, on/off ratio, conductance states, cycle-to-cycle variation, device-to-device variation, read noise, and device failure ratio in the array, etc. are discussed in offline learning and online learning respectively. Based on the above systematical investigation, the optimization direction of the memristor synapse device for hardware neuromorphic system is proposed.

Key words: Memristor Artificial synapse Multilayer perceptron Neural network Handwritten font recognition

目录

1绪论

1.1引言

在大数据的时代背景下,我们不得不面对一个非常严峻的现实问题,那就是数据的量越来越多,数据的类型越来越多,从以前主要的文本信息,到后来的图像信息、音频信息、视频信息,再到现在和未来各种传感器信息,数据的种类是五花八门,多种多样,数不胜数的。因此,为了从大量数据中提取有用信息,人工智能算法工程师们提出了各种用于大数据处理的算法,其中使用分层神经网络结构的深度学习算法[1]显示了比传统机器学习算法更加优异的性能。深度学习算法在图像分类、语音识别、自然语言处理、自动驾驶、医疗辅助诊断、棋盘游戏等领域具有广泛的应用前景。目前,深度学习算法主要指卷积神经网络[2](CNN),堆叠自动编码器[3](Stackedautorencoder),深度信念网络[4](Deepbeliefnetwork)等。然而,深度学习算法却需要消耗大量的计算机资源来训练网络中的权重。例如:Google开发的堆叠自动编码器算法[4],可以从来自YouTube视频中的1000万张图片中成功识别出猫的面部。然而,这项简单的任务却需要16000个处理器同时工作3天的时间来训练网络中的权重,并消耗大约100kW的功率。因此,大幅度的提高硬件速度和能效比对深度学习算法的大规模普及和应用至关重要。基于传统冯·诺依曼架构的硬件系统,如:CPU、GPU,由于“冯·诺依曼瓶颈”的存在[5],数据需要不断的在计算单元与存储单元之间来回的搬运,从而造成大量的时间和能量的浪费。为了克服这个困难,研究人员提出了神经形态计算[6]用来替代传统的冯·诺依曼架构。神经形态计算是一种受大脑认知功能启发的新型计算范式,能够更加高效的进行并行和分布式计算,通过存储与计算融合的方式,降低计算功耗。目前,神经形态计算研究的重要分支就是基于新型非易失存储器件的神经网络硬件加速器。忆阻器因具有高密度、高速、低功耗、易集成、与CMOS工艺兼容等优势[7],是极具潜力的神经网络中的突触基本单元,因此探索忆阻器件的非理想特性对神经网络性能的影响,对实现基于忆阻器的神经网络硬件系统具有重要意义。

1.2忆阻器简介

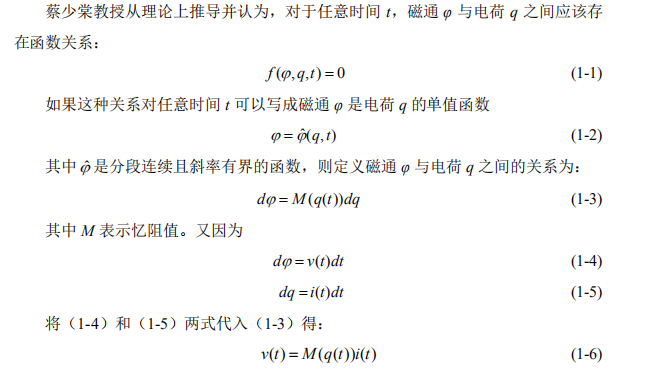

1971年,美国加州大学伯克利分校的蔡少棠教授根据电压v、电流i、电荷q和磁通φ四个基本的电学变量,利用对称性原理在理论上推测出,除了电阻R、电容C和电感L之外,还存在第四种二端基本电路元件,可以表征q与φ之间的关系[8].如图1-1(a)所示,电阻定义为电压与电流的导数dv=Rdi,电容定义为电荷与电压的导数dq=Cdv,电感定义为磁通和电流的导数dφ=Ldi,那么第四种二端基本电路元件就应该定义为磁通和电荷的导数dφ=Mdq,于是蔡少棠教授就把它命名为忆阻器(Memristor,memory-resistor),并用符号M表示。

所以,忆阻器应该满足这个数学定义M(q(t))=v(t)/i(t),其与电阻的量纲一致,可以认为是一个符合欧姆定律的动态电阻,其状态与时间t有关。综上,忆阻器可以看做一个非线性电阻,其记忆住随时间流经过它的电荷总量q,即:忆阻器的值由流过它的电流对时间的积分来决定的。自忆阻器的概念提出以后,经过30多年人们一直未能从物理上实现忆阻器件。直到2008年,惠普实验室在《Nature》杂志上发文《Themissingmemristorfound》,他们认为Pt/TiO2/Pt三明治叠层结构器件在电压扫描的过程中出现的“8”字挤压的回线阻变现象,如图1-1(b),就是忆阻器[9].

自此,越来越多的研究人员开始转向忆阻器的研究,并且在各种不同的材料体系和结构中发现了忆阻现象。随着研究的深入,研究人员对不同材料中的阻变机理有了更深入的认识和理解,并建立了各种不同物理模型来解释忆阻现象,其中被广泛接受和认可的模型是导电细丝模型和非导电细丝模型。

如图1-2(a)所示,导电细丝模型是在电压的驱动下,金属氧化物(如:HfOx[10],AlOx[11],WOx[12],TaOx[13]和TiOx[14])中的缺陷(氧空位)能够通过形成和断开导电细丝的原理实现电阻转变的过程,即:施加正向电压时,金属氧化物中的缺陷(氧空位)能够在器件的两端形成导电细丝,电阻转变为低阻态;在施加反向电压时,导电细丝能够断开,电阻又转变为高阻态。

基于导电细丝模型的忆阻器件往往具有速度快、功耗低、与CMOS工艺兼容的优点。然而,由于导电细丝的形成(SET)过程是突然的,使得电导的增加非常难以控制,而传统的解决方法是通过施加限制电流的方式来控制导电细丝的生长,但是想要在神经形态计算中采用多级限制电流的方式来控制导电细丝的生长,往往是不可行的,因为这无疑会大大增加外围电路的复杂度。如图1-2(b)所示,非导电细丝模型的电阻转变机理,是源于整个器件区域上界面处的肖特基势垒或隧道势垒的场变化引起的电阻转变过程[15].基于这一机理的忆阻器件能够很好的实现渐进的电导调节,非常适合用于模拟突触。目前,已有大量文献报道了基于这一模型的RRAM模拟突触器件,如:Ag:a-Si[16],TaOx/TiO2[17,18],PCMO[19,20].尽管基于该模型的忆阻器件能够有效的实现电导渐变调控,但是,由于缺陷运动引起的势垒非线性的变化,使得电导渐变调控曲线具有明显的不对称和非线性特性。而这些非理想的渐变调控特性必将对神经网络的准确性产生一定的影响。

1.3基于忆阻器的神经网络研究现状

如上所述,为了应对传统的基于CMOS技术的神经网络硬件平台在面积、速度、功耗以及“冯·诺依曼瓶颈”等方面的挑战,研究人员希望利用新型的非易失存储器件忆阻器来构建神经网络硬件加速器,从而大幅度的提高神经网络硬件系统的性能。一方面,忆阻器具有高速、高密度以及多值特性,能够更好的模拟突触,从而减少神经网络的硬件面积,另一方面,基于忆阻器的交叉阵列不仅能替代传统的SRAM阵列用来存储权重,而且还能够实现并行的矩阵向量乘法运算和权重更新操作。与具有6个或8个晶体管的二进制SRAM单元相比,单个忆阻器件就能存储二进制信息,并且单个忆阻器件还具有多值存储的功能,这意味着基于忆阻器的神经网络硬件系统能够大幅度的减小神经网络芯片的面积。与SRAM阵列顺序的写入与读取方式不同,基于忆阻器的叉阵列能够实现并行的权重写入操作,同时还具有计算能力,能够实现并行的矩阵向量乘法运算,这表明基于忆阻器的硬件神经网络具有存储与计算融合的能力,能够大幅的加速神经网络,并且能够实现在线学习过程。目前,基于忆阻器的神经网络研究还处于起步阶段,大量的文献报道还是基于少量忆阻器件的测试数据与软件仿真相结合的研究方式。根据现有的文献报道,基于忆阻器的神经网络研究主要有三个方向:

(1)基于忆阻器的脉冲神经网络[22-29](SNN)脉冲神经网络主要受神经科学的启发,主要表现为信息的编码方式是基于脉冲时刻的神经编码,突触权重的更新方式是基于神经科学上已验证的生物学习规则,如:活动时序依赖的突触可塑性(Spiking-timingdependentplasticity,STDP)[21].STDP学习规则表明如果突触前神经元比突触后神经元更早的激活,则突触的权重会减小,反之则增大,并且当两个神经元之间激活的时间差越接近,突触权重的变化量越大。目前,基于忆阻器的脉冲神经网络主要采用STDP无监督[22-25]或STDP有监督[26-29]的学习算法来训练神经网络,但是受制于神经科学的研究进展,如何有效的根据STDP规则来更新神经网络中的权重依然是脉冲神经网络需要探索和解决的主要问题。

(2)基于忆阻器的多层感知机(MLP)[30-35]和卷积神经网络(CNN)[36-40]不同于SNN,MLP和CNN神经网络的输入信息采用基于脉冲频率的编码方式,突触权重的更新方式采用更加有效的有监督的反向传播算法,训练误差能够从输出神经元层逐层反馈到输入神经元层。基于这种信息编码和权重学习规则的神经网络在训练与推断的过程中涉及大量的矩阵向量乘法运算。为了加速矩阵向量乘法运算(乘法和累加计算)以及最小化硬件中数据移动的能量消耗,基于忆阻器的硬件神经网络,通过欧姆定律和基尔霍夫电流定律,在忆阻器交叉阵列中实现并行的矩阵向量乘法运算以及原位的权重更新与存储功能。以清华大学吴华强团队的忆阻器神经网络人脸识别工作为例,基于1T1R集成结构的忆阻器交叉阵列实现了1层的感知机神经网络,用于识别9张灰度人脸照片中不同的3个人[32].

如图1-3所示,神经网络的输入层神经元与1T1R忆阻器阵列的位线(BL)对应,输入信息转换为电压信号。神经网络的输出层与1T1R忆阻器阵列的选择线(SL)对应,输出加权求和后的电流值。神经网络中的神经元之间连接的突触与阵列中交叉点处的忆阻器件对应,权值大小对应忆阻器件的电导值大小。1T1R忆阻阵列的字线(WL)外接控制信号,用于实现忆阻阵列行选通操作,当进行前向推断过程时,WL全接高电平,所有1T1R单元全部打开,然后在BL施加输入的电信号,SL输出加权求和后的电流信号,以此实现并行的加权求和运算。当权重更新时,WL通过外围译码电路进行逐行的打开,然后在BL和SL施加相应的电信号,对权重进行更新。如图1-3(b)所示,输入的人脸图片按照像素灰度值大小编码为电脉冲个数,如:像素值为255,则对应着255个电脉冲。因此实际上,该研究中完整的加权求和过程还需要对255个周期中输出的电流进行累加计算。

上述文献实现的网络比较简单,只有一层,不存在层与层之间的通信,同时由于实现的任务比较简单,也没有考虑正负权重与忆阻器件电导之间的映射方式。下面再通过马萨诸塞大学杨建华团队的研究工作[33],简单介绍下层间通信与正负权重表示。如图1-4(b)所示,为了实现正负权重表示,首先将忆阻器阵列扩展一倍,一部分用于存储正的权重,一部分用于存储负的权重,然后在输入信息时,两部分权重对应的列分别输入相反的电压信号。为了实现层间通信,在每一层的输出行上设计相应的外围电路,可以将加权求和的电流转换为电压信号,并实现线性和带有阈值的激活函数,从而作为下一层的输入电压信号。此种方式,将输入信息编码为了电压的幅值,只需一个周期便能完成加权求和过程。但是,由于忆阻器件的非线性I-V特性,采用电压幅值的编码往往会对加权求和的电流产生较大的计算误差,并且神经元电路相对固定,难以实现其他类型的激活函数。此外,基于两个忆阻器件的突触在实现在线学习的过程中,需要对忆阻器电导进行预读取,才能判断当前应该改变正向电导的大小还是负向电导的大小。所以,基于忆阻器的MLP和CNN神经网络,虽然都是通过忆阻器阵列实现并行的矩阵向量乘法运算,但是基于不同的输入信息编码方式以及外围神经元电路的设计方式,在实现神经网络推断和权重更新方式上具有很大的不同。

(3)基于忆阻器的二值神经网络(BNN)[42-44]二值神经网络[41]是在CNN的基础上对权重和激活函数做二值处理,即:将权值限制为+1和-1,激活函数输出值限制为+1和0或者+1和-1.由于二值神经网络在训练的过程中任然需要对实数型的权值和激活函数值进行求梯度,并以此更新权值,所以基于忆阻器的二值神经网络主要用于离线学习过程。相对于忆阻器不稳定的模拟特性而言,实现可区分的两个权值状态的忆阻器技术要稳定很多。因此,基于忆阻器的二值神经网络实现方案在短期内更具可行性,以亚利桑那州立大学ShimengYu团队的一项研究工作为例[44],基于忆阻器的二值神经网络有两种形式,一种是串行的,一种是并行的。如图1-5(a)所示,为串行的忆阻器二值神经网络,该方式用一个忆阻器表示突触,高阻代表权重-1,低阻代表权重+1,WL译码器每次开启一行,进行并行的乘法运算,通过输出端的电流模式读出放大器(Currentmodesenseamplifier,CSA)判断输出的是+1或-1,然后经过加法器将每一行的输出求和,最后通过一个比较器判断激活函数的输出值0或1.如图1-5(b)所示,为并行的忆阻器二值神经网络,该方式用两个忆阻器表示一个突触单元,左边忆阻器为低阻,右边为高阻时,代表权重+1,左边忆阻器为高阻,右边为低阻时,代表权重-1,CSA两端分别接突触单元对应的两列忆阻器,当进行读操作时,WL选择开关一次性全打开,进行并行的乘法和累加计算,然后通过CSA直接得出激活函数的输出值0或1.基于忆阻器的二值神经网络硬件化,能够有效的降低硬件的面积、功耗,并且忆阻器的二值特性比较成熟,是很有前景实现的忆阻神经网络方案。

1.4本课题的研究意义与主要研究内容

本论文研究课题聚焦于忆阻器的神经网络研究,主要利用忆阻器件的模拟特性和忆阻器阵列实现最简单的多层感知机(Multi-LayerPerception,MLP)神经网络,结合随机梯度下降算法(StochasticGradientDescent,SGD),面向MNIST手写字体数据集识别任务,设计了神经网络的硬件结构、突触表示方式、输入信息编码方式,以及神经网络算法到硬件的映射方式,编写基于忆阻器和忆阻器阵列的神经网络离线和在线学习程序,然后通过仿真的方式探索忆阻器的不同特性参数对手写字体识别率的影响,最后根据仿真结果提出忆阻器件用于实现神经网络的参数优化方向。以下为本论文内容的具体安排:第一章首先介绍了大数据时代背景下,深度神经网络是处理与提取数据有用信息的有效方式,但基于现有冯·诺依曼架构的硬件平台难以满足神经网络对计算资源的需求,急需一种新型的神经网络硬件加速平台,然后介绍了忆阻器的基本概念和模型,以及基于忆阻器神经网络的特点、优势及研究进展,最后说明了本课题研究的主要内容。第二章首先介绍了人工神经网络的基本概念,包括神经元模型、MLP神经网络结构、激活函数、随机梯度下降算法(SGD)的前向和后向传播的数学计算过程,然后设计了面向MNIST手写字体数据集识别的2层的感知器神经网络,并通过纯软件计算结果,选取了较优的隐藏层神经元数目和权重更新的学习率。第三章首先定义了一种常用的忆阻器渐变特性数学模型,并基于该模型量化了忆阻器电导调控渐变特性曲线中的非理想参数,如:非线性、电导阶数、器件间不一致性、窗口比等,然后描述了忆阻器阵列实现矩阵向量乘法的基本原理和阵列中权重更新的操作方式,最后设计了基本的硬件模块来实现神经网络算法到具体硬件之间的映射过程。第四章根据神经网络算法到忆阻器组成的硬件之间的具体映射方式,实现了基于忆阻器的神经网络离线和在线学习的仿真程序,并通过仿真探讨了忆阻器件的不同参数特性对手写字体识别率的影响。最后一章对整个研究工作进行了总结,并展望了未来可以进行的工作方向。

【由于本篇文章为硕士论文,如需全文请点击底部下载全文链接】

3基于忆阻器的神经网络硬件结构设计

3.1忆阻器模型的建立

3.2基于忆阻器阵列的加权求和与权重更新

3.3基于忆阻器的神经网络硬件与学习算法的映射

3.4本章小结

4基于忆阻器的神经网络软件设计与仿真

4.1基于忆阻器的神经网络结构设计

4.2基于忆阻器的神经网络离线学习仿真

4.3基于忆阻器的神经网络在线学习仿真

4.4神经网络的鲁棒性与自适应性

4.5实际器件测量数据在线学习仿真

4.6本章小结

5总结与展望

5.1总结

忆阻器作为下一代新兴非易失存储器,不仅具有高速、高密度、低功耗、易集成、与CMOS工艺兼容等优点,而且其模拟特性可以用于实现神经网络学习算法中权重的表示,并且可以在忆阻阵列中实现矩阵向量乘法运算。本文探究了基于忆阻器的模拟特性在用作神经网络权重的表示和计算过程中,由于忆阻器件电导渐变调控的非理想参数特性对神经网络识别率的影响,从而确定模拟忆阻器件的参数优化方向。现将研究工作主要成果和结论总结如下:

1)本工作基于忆阻器阵列实现矩阵向量乘法的基本原理,设计了阵列中输入信息的编码方式、权重到器件电导的映射方式、以及必要的外围电路基本模块,理论上可以实现基于忆阻器特性的矩阵向量乘法运算,并结合神经网络的鲁棒性,从而通过忆阻器阵列加速神经网络的训练过程。2)本工作基于忆阻器阵列能够并行的进行矩阵向量乘法运算和权重更新操作,设计了2层的感知机神经网络模型,并用C++编程语言编写基于忆阻器阵列的随机梯度下降算法计算过程,实现了基于忆阻器的MLP神经网络仿真平台。

3)本工作通过离线学习和在线学习的仿真,发现忆阻器电导窗口大小对神经网络的性能至关重要。离线学习中电导窗口比至少要有30倍,在线学习至少需要10倍以上。而电导阶数大小对离线学习没有太大影响,最低只需1位或2位的电导精度就足够了,但对于在线学习却至少需要5-6位精度的电导阶数。

4)电导渐变的非线性直接影响了神经网络在线学习的性能,但是较好的电导增加与减小过程的对称性能够容忍非线性的影响。所以,器件优化除了改善非线性外,还可以改善电导增加与减小过程的对称性。较差的器件一致性与循环一致性往往对神经网络的性能有害,应该设法提高器件一致性与循环一致性。

5)神经网络具有鲁棒性和自适应性,在线学习过程中,至少能够容忍忆阻器阵列中>10%的器件失效率,并且可以通过将故障器件置于高阻态(或断开),进一步提升可以容忍的失效率(>25%)。

5.2展望

本论文研究的内容比较粗浅,工作还很初步,存在许多不足之处。并且,本领域的其他研究者也开展了不少类似的研究工作,但是,由于目前还没有大规模的忆阻器阵列的量产,本领域的研究方法主要还是通过少量忆阻器件的实验测量数据以及软件仿真的方式来说明问题,并且不同的研究人员可能设计的软件算法到硬件的映射方式不同,得到的结果也不尽相同。所以,本工作对于实验室器件方面的研究还是有一定的指导意义,并且该工作还可以继续深入的进行研究,主要研究目标如下:

1)本工作主要针对基于LiSiOx忆阻器的实验数据做了相应的仿真研究,未来需要对更多类型的忆阻器件(如具备量产前景的HfOx忆阻器)进行电导调控行为的大规模测量和数据统计,获得更普适的电导行为模型相应仿真程序,进一步深入阐明器件实际行为对神经网络性能的影响。

2)本工作在设计的仿真程序中仅仅利用理想的忆阻器阵列做计算,实际应用中由于阵列中各种的漏电流问题,忆阻器阵列往往是由1T1R或1S1R构成的,因此,基于1S1R和1T1R的阵列计算也可以进行研究,同时还可以考虑阵列中其他因素(如寄生效应、压降问题)的影响。

3)本工作只是简单设计了忆阻阵列实现神经网络算法的基本硬件模块,对于具体模块对应的电路结构没有涉及到,未来可以从电路层面考虑,对该工作进行优化和扩展,并且探索电路方面的相关特性,如功耗、延时、面积等。

致谢

参考文献\

【由于硕士论文篇幅较长,此页面不展示全文,如需全文,请点击下方下载全文链接】